一键超频

实现目的

单片机超频的主要目的是提高处理器的工作速度,以获得更高的性能和处理能力。超频可以使单片机在特定的应用场景下执行更多的指令,加快数据处理和运行速度,从而提升整体系统性能。

芯片超频能做什么:

- 加快运算速度:超频可以使单片机在相同的时间内执行更多的指令,从而加快程序的运行速度。

- 提高响应速度:对于一些需要实时响应的应用,超频可以减少处理器的响应时间,使系统更加敏捷和快速响应外部事件。

- 处理更复杂的任务:通过超频,单片机可以处理更大规模、更复杂的任务,例如高清视频处理、实时图像处理等。

- 提高系统性能:在某些应用场景下,超频可以提高整个系统的性能,使其能够更好地满足需求。

在获取更高的运算速度的同时,超频也会引入更高的功耗和温度,有可能导致稳定性问题。因此,在进行超频操作时,不建议将芯片主频过分提高,同时需要谨慎注意系统的工作环境和散热条件,以确保系统的安全和可靠性。

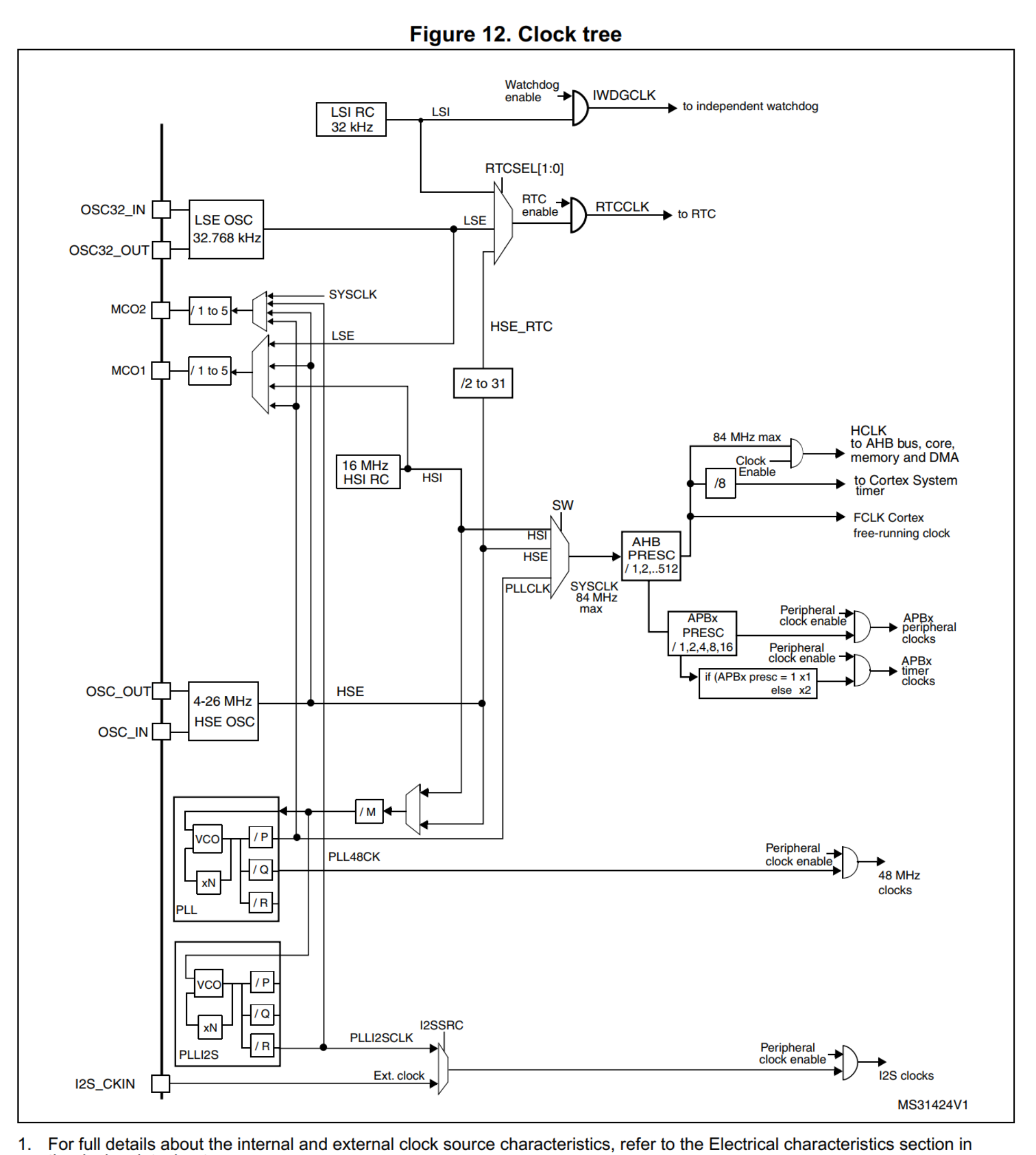

时钟树

上图为STM32F401的时钟树,本节主要分析芯片总线的时钟逻辑。

时钟输入

HSE时钟,即高速的外部时钟。

来源:有源晶振( 1-50M)、无源晶振( 4-26M)

特点:能够提供高精度、稳定的时钟信号,频率可调,适用于高性能应用。依赖于外部晶体振荡器,可能受到外部环境和干扰的影响,需要额外的硬件支持以及较好的电磁兼容设计,较高的功耗。

HSI时钟,即高速的内部时钟。

来源:芯片内部,大小为16M,当HSE故障时,系统时钟会自动

切换到HSI,直到HSE启动成功。

特点:时钟精度相对较低,不适用于高性能和高精度的应用。

在实际应用中,一般均选用HSE时钟作为芯片总线时钟输入源。

锁相环时钟

锁相环时钟(PLL)是一种常用的时钟源和时钟倍频器,主要用于提供高频率的时钟信号。锁相环时钟能够提供高精度的时钟源,锁相环时钟可以通过倍频器将输入的参考时钟信号(HSE/HSI)进行倍频,生成更高频率的时钟信号,使单片机可以以更高的时钟频率运行,提供更高的计算和数据处理能力。其次,锁相环时钟可以作为单片机内部各个外设的主时钟源。通过将锁相环时钟与外设和处理器的时钟信号同步,可以确保它们以相同的基准进行工作,实现数据的准确同步和协调操作。

主 PLL 有两路的时钟输出,第一个输出时钟 PLLCLK 用于系统时钟, F407 里面最高是 168M,第二个输出用于 USB OTG FS 的时钟(48M)、 RNG 和 SDIO 时钟(<=48M)。专用的 PLLI2S 用于生成精确时钟,给 I2S 提供时钟。

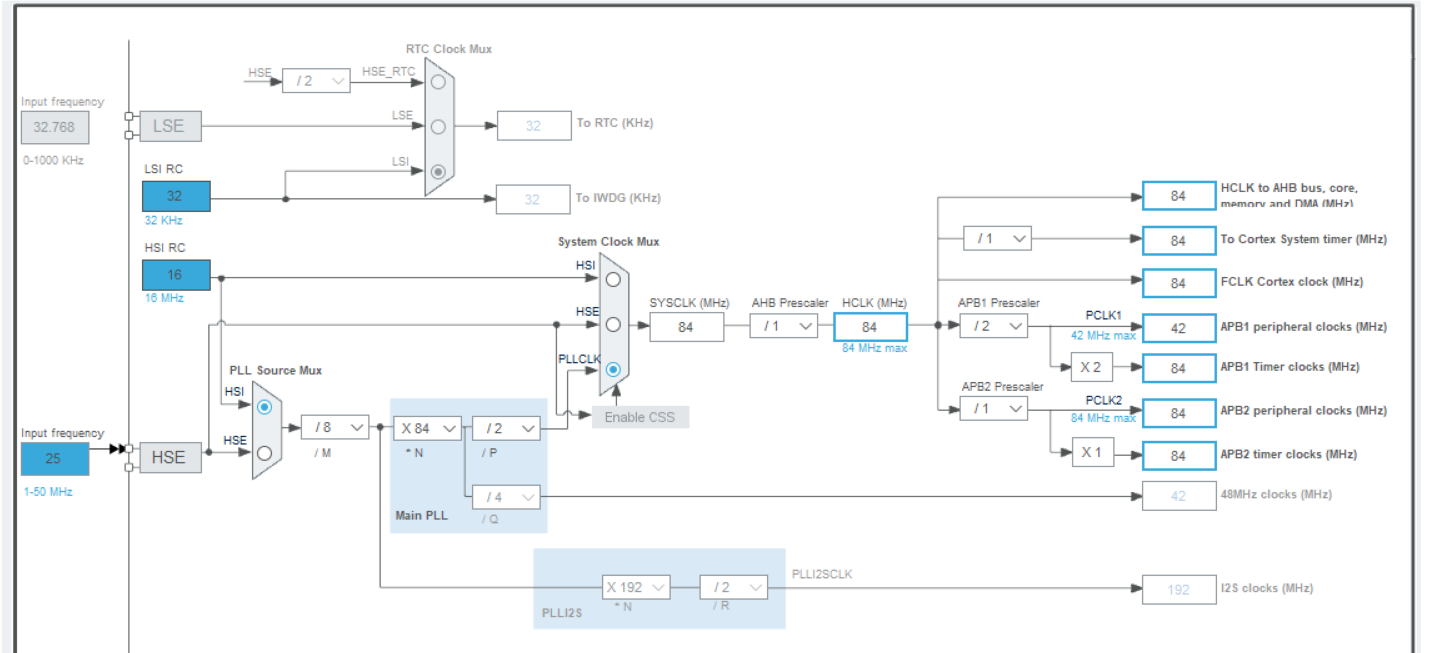

HSE 或者 HSI 经过 PLL 时钟输入分频因子 M(263)分频后,成为 VCO 的时钟输入, VCO 的时钟必须在 12M 之间,一般将VCO 输入时钟配置为1M。

VCO 输入时钟经过 VCO 倍频因子 N 倍频之后,成为 VCO 时钟输出, VCO 时钟必须在 192~432M之间。若配置 N 为336,则 VCO 的输出时钟等于 336M。如果要把系统时钟超频,就得在 VCO 倍频系数 N 这里进行改动。

VCO 输出时钟之后有三个分频因子,锁相环时钟经PLLCLK 分频因子p输出到系统时钟, p 可以取值 2、 4、 6、 8, 将配置为 4,则得到PLLCLK=84M。

tips:

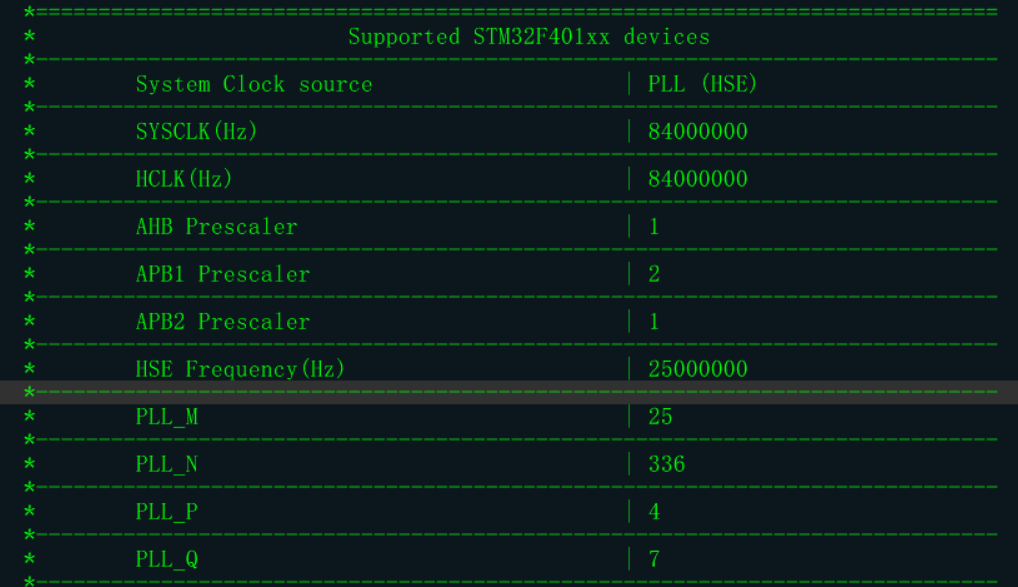

以我使用的F401核心板为例,HSE为12M晶振,使 PLL_M = 12,PLL_N = 336,PLL_P = 4,得到系统时钟输入为84MHz。此为正常情况下系统时钟的最大输入值。通过修改PLL_N的值,使系统时钟输出超过84MHz即为超频。

SYSCLK = HSE / PLL_M * PLL_N / PLL_P

系统时钟

系统时钟来源可以是: HSI、 PLLCLK、 HSE,具体的由时钟配置寄存器 RCC_CFGR 的 SW 位配置。上述操作系统时钟配置为: SYSCLK = PLLCLK =84M。如果系统时钟是由 HSE 经过 PLL 倍频之后的 PLLCLK 得到,当 HSE 出现故障的时候,系统时钟会切换为 HSI=16M,直到 HSE 恢复正常为止。

总线时钟

AHB总线时钟:

系统时钟 SYSCLK 经过 AHB 预分频器分频之后得到时钟叫 AHB 总线时钟,即 HCLK,分频因子可以是:[1,2,4, 8, 16, 64, 128,256, 512],具体的由时钟配置寄存器 RCC_CFGR 的 HPRE 位设置。片上大部分外设的时钟都是经过 HCLK 分频得到。

APB总线时钟:

- APB2总线时钟:

PCLK2 由 HCLK 经过高速 APB2 预分频器得到,分频因子可以是:[1,2,4, 8, 16]。PCLK2 属于高速的总线时钟,片上高速的外设挂载到这条总线上。

- APB1总线时钟

APB1 总线时钟 PCLK1 由 HCLK 经过低速 APB 预分频器得到,分频因子可以是:[1,2,4, 8, 16]。 PCLK1 属于低速的总线时钟,片上低速的外设挂载到这条总线上,

至此,已经完成对片上总线时钟的输入输出的溯源,下面进行相应代码的编写。

Tips:

这里插入部分STM32的启动文件的部分介绍,启动文件由汇编编写,是系统上电复位后第一个执行的程序。主要做了以下工作:

1. 初始化堆栈指针 SP=_initial_sp

2. 初始化 PC 指针 =Reset_Handler

3. 初始化中断向量表

4. 配置系统时钟 (SystemInit函数)

5. 调用 C 库函数 _main 初始化用户堆栈,从而最终调用 main 函数去到 C 的世界

根据程序的执行顺序,在程序来到main函数之前,SystemInit()函数已经完成对系统时钟的初始化(SystemInit()在system_stm32f4xx.c中定义),如果想修改系统时钟,可自行编写程序修改,重新设置系统时钟,同时可以选择使用HSE还是HSI。

注意 :由于在 PLL 使能后主 PLL 配置参数便不可更改,而系统上电后会自动进行初始化,因此在对HES重新初始化之前,需要将system_stm32f4xx.c中的line514:SetSysClock();注释掉,否则HSE重新初始化之后不生效。

将SetSysClock()注释之后可以仿照该函数编写自己的时钟初始化函数。

void HSE_SetSysClock(uint32_t PLLM, uint32_t PLLN, uint32_t PLLP, uint32_t PLLQ)

{

ErrorStatus HSE_ErrorStatus=ERROR;

/* 复位RCC的所有寄存器 */

RCC_DeInit();

/* 使能 HSE */

RCC_HSEConfig(RCC_HSE_ON);

/* 等待HSE启动 */

HSE_ErrorStatus=RCC_WaitForHSEStartUp();

if(HSE_ErrorStatus==SUCCESS)

{

/* 选择电压调节器的模式为1 */

RCC->APB1ENR |= RCC_APB1ENR_PWREN;

PWR->CR |= PWR_CR_VOS;

/* 配置三个总线的分频因子 */

RCC_HCLKConfig(RCC_SYSCLK_Div1); //AHB总线 1 分频

RCC_PCLK1Config(RCC_HCLK_Div2); //APB1总线 2 分频

RCC_PCLK2Config(RCC_HCLK_Div1); //APB2总线 1 分频

/* 配置主PLL */

RCC_PLLConfig(RCC_PLLSource_HSE, PLLM, PLLN, PLLP, PLLQ);

/* 使能主PLL */

RCC_PLLCmd(ENABLE);

/* 等待主PLL稳定 */

while( RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET )

{}

/* 配置FLASH预取指,指令缓存,数据缓存,等待周期 */

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

/* 选择主PLL为系统时钟 */

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

/* 确保主PLL被选为系统时钟 */

while( RCC_GetSYSCLKSource() !=0x08 )

{}

}

else

{

/*HES启动失败,在这里添加处理代码*/

}

}

总结

超频实际上是提高芯片总线主频,获取更高的运算速率,超频会对阻塞式延时函数的延时时间造成一定影响(原定延时1s实际延时不足1s),具体效果可以通过LED灯闪烁的快慢体现。